良いPCBボードの作り方

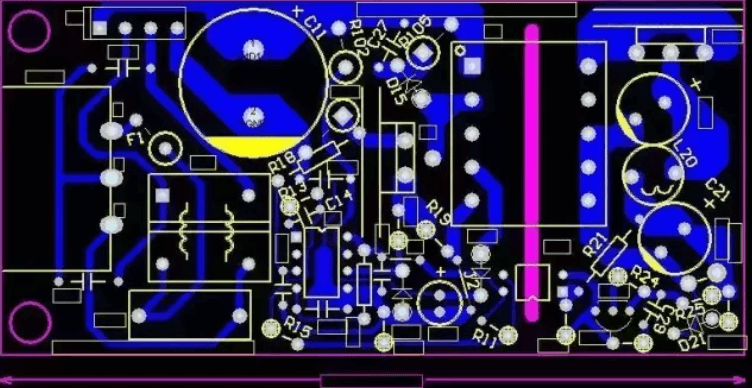

誰もがPCBの回路図を行うために知っている実際のPCBに設計されており、このプロセスを過小評価しないでください、達成することが困難であるか、いくつかのPCBメーカーは、それらを実現することができ、他の人が達成していない工学の実用化の原則に多くのものがあります、それはPCBを作ることは難しいことではありませんが、良いPCBボードを作ることは簡単なことではありません。マイクロエレクトロニクスの分野では、高周波信号と微弱信号の処理が2大難関である。この点で、PCB製造のレベルは特に重要である。同じ回路図設計、同じコンポーネント、異なるPCB工場はPCBが異なる結果を持って作るので、どのように良いPCBボードを作るには?

1.デザイン目標を明確にする

設計タスクを受け取った、最初に設計目標をクリアする必要があります、一般的なPCBボード、高周波PCB、小信号PCBまたはPCBの高周波と小信号の両方があり、それが一般的なPCBであれば、合理的なレイアウトを行う限り、整頓、機械的なサイズの正確な、それは大丈夫でしょう。

基板上に40MHzを超える信号線がある場合、これらの信号線には特別な配慮が必要である。周波数が高くなれば、トレースの長さにはより厳しい制約が生じる。分散パラメータ・ネットワーク理論によれば、高速回路とそのトレースとの相互作用は、システム設計において無視できない決定的な要因である。伝送速度の高速化に伴い、信号線路の対向はそれに応じて増加し、隣接する信号線路間のクロストークは正比例して増加する。一般的に、高速回路の消費電力と放熱量も非常に大きいため、高速プリント基板を作る際には十分な注意が必要です。

基板上にミリボルト、あるいはマイクロボルトの微弱信号がある場合、これらの信号線には特別な注意が必要だ。微弱信号は弱すぎるため、他の強い信号の干渉を受けやすい。シールド対策が必要になることが多いが、そうしないとS/N比が大幅に低下する。そのため、有用な信号がノイズにかき消され、効果的に取り出すことができなくなる。

ボードのデバッグは、設計段階でも考慮されるべきであり、テストポイントの物理的な位置、テストポイントのアイソレーション、その他の要因も無視できない。

さらに、ボードの層数、使用部品のパッケージング、ボードの機械的強度など、いくつかの他の関連要因を考慮する必要があります。PCBボードを作る前に、設計の目標について明確なアイデアを持っている必要があります。

2.使用部品のPCBレイアウトとPCB配線要件を理解する。

ご承知のように、LOTI や APH で使用されるアナログ・アンプのように、レイアウトや配線に特別な要件がある特殊な部品もあり、そのような部品にはスムーズでリップルの少ない電源が必要です。アナログ小信号部は、電源デバイスからできるだけ離して配置する必要がある。OTIボードでは、小信号増幅部には迷走電磁干渉を遮蔽するための遮蔽カバーが特別に装備されている。NTOIボードに使用されているGlinkチップはECLプロセスを採用しており、消費電力が大きく発熱も大きい。従って、レイアウトの放熱問題には特別な配慮が必要である。自然放熱を採用する場合、Glinkチップは空気の循環が比較的スムーズで、放出される熱が他のチップに大きな影響を与えない場所に配置する必要があります。ボードにスピーカやその他の大電力デバイスが搭載されている場合、電源に深刻な汚染を引き起こす可能性があり、これにも十分な注意を払う必要があります。

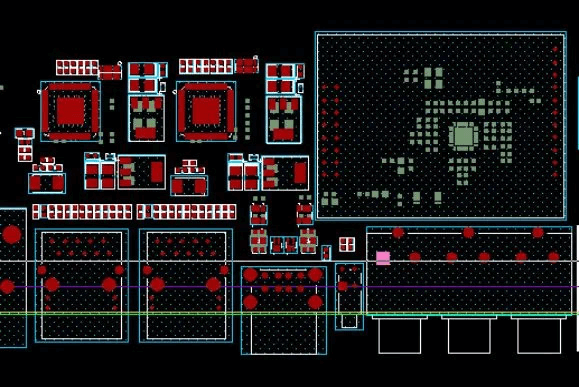

3.コンポーネントの配置に関する考慮事項

部品のPCB設計で考慮すべき最初の要因の一つは電気性能である。部品の実際のサイズ(占有面積と高さ)と部品間の相対的な位置は、回路基板の電気性能と生産と設置の実現可能性と利便性を確保するために考慮しなければならない。密接に接続された部品はできるだけ一緒に配置し、特にいくつかの高速ラインについては、できるだけ短くする。電源信号と小信号部品を分離する。回路性能を満足させることを前提に、部品がきれいに配置され、美しく、テストしやすいことを考慮し、基板の機械的なサイズ、ソケットの位置なども真剣に検討する必要がある。

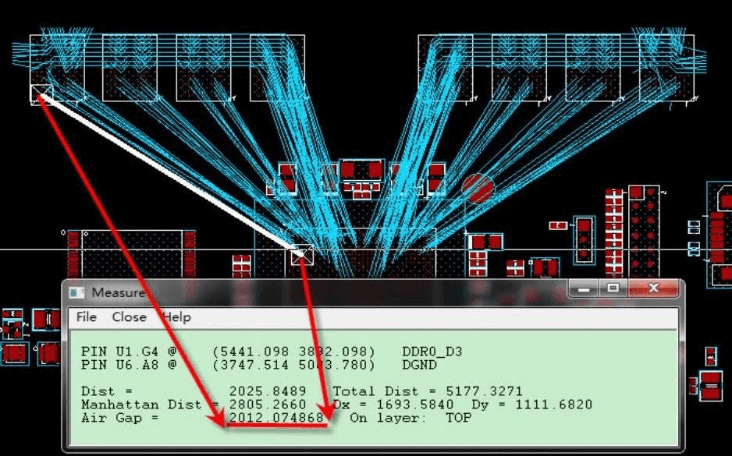

高速システムにおける接地と相互接続の伝送遅延時間は、システム設計において考慮すべき最初の要因でもある。信号線上の伝送時間は、特に高速ECL回路において、システム全体の速度に大きな影響を与える。集積回路ブロック自体の速度は非常に高速ですが、基板上の通常の相互接続の使用による遅延時間の増加(線路長30cmごとに約2nsの遅延)は、システム速度を大幅に低下させます。

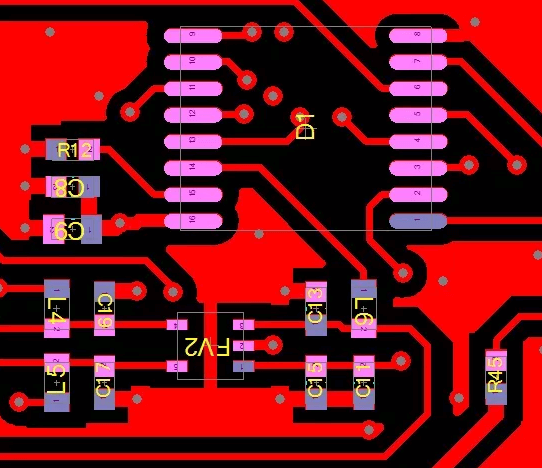

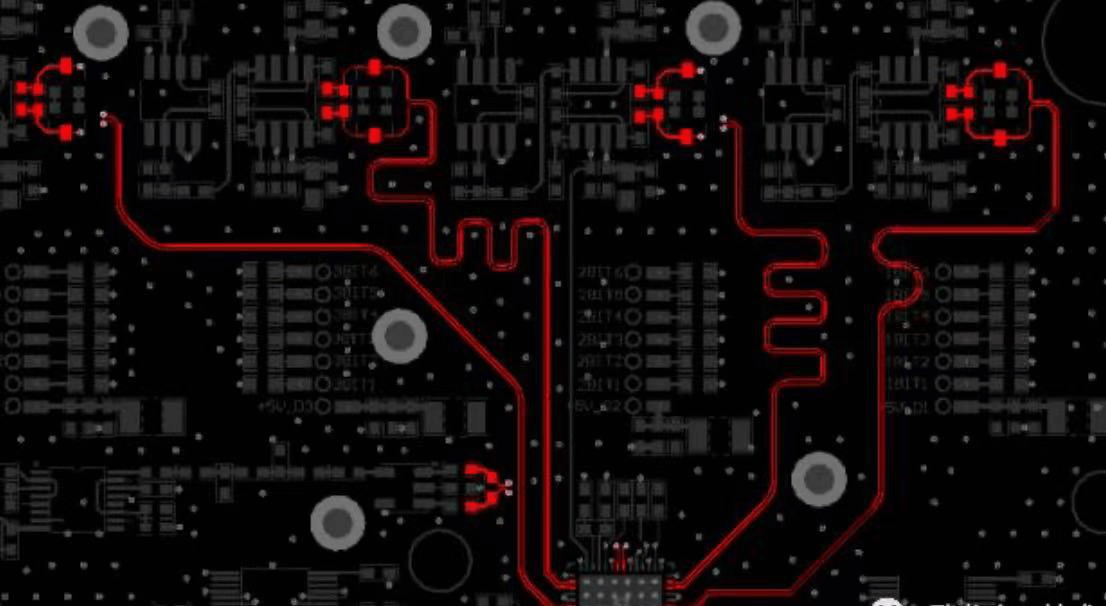

4.PCB配線

PCB配線は、PCB設計全体の中で最も重要な手順です。これはPCBボードの性能に直接影響します。PCBの設計プロセスでは、配線は主に以下の原則に従って行われます:

(1)一般的に、回路基板の電気的性能を確保するために、電源ラインとグランドラインを最初に設計する必要があります。可能な限り、電源、グランドラインの幅を広くしてみて、それは電源ラインよりも広いことが最善であり、それらの関係は、グランドライン>電源ライン>信号線であり、通常、信号線の幅は次のとおりです:0.2〜0.3ミリメートル、最大0.05〜0.07ミリメートルの最小幅、電源ラインは、一般的に1.2〜2.5ミリメートルである。デジタル回路用のPCBは、回路を形成するために広いグランド導体を使用することができます、つまり、グランドグリッドを形成する(アナログ回路のグランドは、このように使用することはできません)。

(2)高周波ラインは、反射干渉を生成しないように、エッジラインの入力と出力は、隣接する平行を避けるために、高度に配置する必要があります。

(3)信号線はループにならないようにし、やむを得ない場合はループをできるだけ小さくする。

(5)フラットケーブルで高感度信号やノイズ帯域の信号を伝送する場合は、「グランド-信号-グランド」を使用する。

(6)生産・保守テストを容易にするため、主要信号にはテストポイントを確保する。

(7)回路図の配線が完了した後、配線を最適化する。同時に、事前のネットワーク検査とDRC検査が正しいことを確認した後、配線されていない部分をグランド線で埋め、広い面積の銅をグランド線として使用する。プリント基板では、使用しない場所をグランドラインとしてグランドと接続する。または、多層基板にして、電源、グランドラインを別レイヤーにする。

PCB配線要件

1.トラック

一般に、信号線幅は0.3mm(12mil)、電源線幅は0.77mm(30mil)または1.27mm(50mil)である。トラックとトラックの間、トラックとパッドの間のスペースは0.33mm(13mil)以上である。トラック密度が高い場合、IC ピン間に幅 0.254mm(10mil)、間隔 0.254mm(10mil)以上のトラックを 2 本使用することも考えられる(推奨しない)。デバイスのピンが密集していて幅が狭いという特殊な状況下では、線幅と線間隔を適切に縮小することができる。

2.パッド

パッドとビアの基本的な要件は、パッドの直径がビアの直径よりも0.6mm以上大きいことである。例えば、普遍的なピンタイプの抵抗器、コンデンサ、集積回路などでは、パッド/ビアのサイズは1.6mm/0.8mm(63mil/32mil)を使用し、ソケット、ピン、ダイオード1N4007などでは、1.8mm/1.0mm(71mil/39mil)を使用する。実用上は、実際の部品の大きさに応じて決定する。条件が許せば、パッドのサイズを適切に大きくすることができる。設計した部品のPCB基板への取り付け穴は、実際の部品ピンのサイズより0.2~0.4mm程度大きくする。

3.Via

通常1.27mm/0.7mm(50mil/28mil);線密度が高い場合、ビアのサイズを適切に小さくすることができるが、小さすぎてはならない。1.0mm/0.6mm(40mil/24mil)が考えられる。

4.パッド、トラック、ビアのスペーシング要件

パッドとビア:≥0.3mm(12mil)パッドとパッド:≥0.3mm(12mil)パッドとトラック:≥0.3mm(12mil)トラックとトラック:≥0.3mm(12mil)高密度トラックの場合:パッドとビア:≥0.254mm(10mil)パッドとパッド:≥ 0.254mm(10mil)パッドとトラック:≥ 0.254mm(10mil)トラックとトラック:≥ 0.254mm(10mil)。

5.ネットチェック、DRCチェック、構造チェック

まず、回路図のPCB設計が正しいことを前提に、生成されたPCBネットワークファイルと回路図ネットワークファイルの物理的な接続関係をチェックし、配線接続関係の正しさを保証するために、出力ファイルに応じて時間内に設計を修正します。

ネットワークチェックが正しく通過した後、PCB設計のDRCチェックを行い、出力ファイルに従って設計を修正し、PCB配線の電気的性能を確保する。最後に、PCBの機械的な取り付け構造をさらにチェックし、確認する必要がある。

PCBレイアウトにおける3つの配線スキル

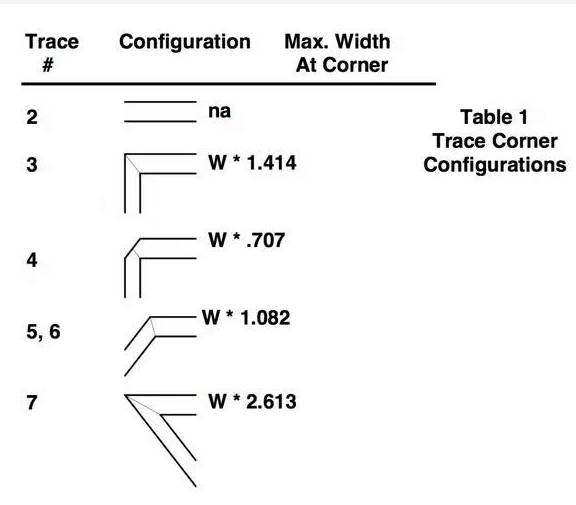

1.直角ルーティング

第一に、コーナーは伝送路上の容量性負荷と等価であり、立ち上がり時間を遅くする。第二に、インピーダンスの不連続は信号の反射を引き起こす。第三に、直角によって発生するEMIである。10GHz以上のRF設計分野では、これらの小さな直角が高速問題の重要な対象になる可能性がある。

2.差動ルーティング

差動信号とは、ドライバが2つの等価な反転信号を送信し、レシーバが2つの電圧の差を比較して、論理状態が「0」であるか「1」であるかを判断するものである。差動信号を伝送する一対のラインは、差動ラインと呼ばれる。通常のシングルエンド信号のルーティングと比較して、差動信号の最も明白な利点は、次の3つの側面に反映されている:1)、外部ノイズの干渉が存在する場合、2つの差動ライン間の非常に良好なカップリングによる高い干渉耐性。受信側は2つの信号の差しか気にしないが、差動信号は同時に両方のラインにカップリングすることができる。そのため、共通の外部ノイズを完全に打ち消すことができる。同様に、2つの信号の極性は逆であるため、それらによって放射される電磁界は互いに打ち消し合うことができる。3)、正確なタイミング位置決め。差動信号のスイッチ変化は2つの信号の交点にあるため、スレッショルド電圧の高低で判断する通常のシングルエンド信号と異なり、プロセスや温度の影響を受けにくく、タイミングの誤差を低減できる。現在普及しているLVDS(低電圧差動信号)は、この小振幅差動信号技術を指す。

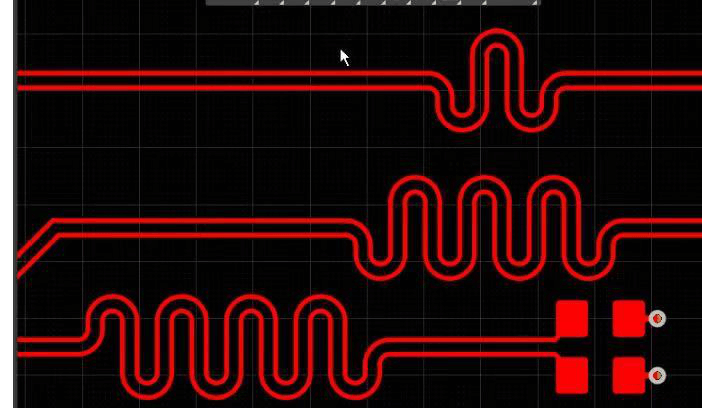

3.カーブ・ルーティング

曲線配線は、PCBレイアウトでよく使用される配線方法の一種です。その主な目的は、システムのタイミング設計要件を満たすために遅延を調整することである。最も重要な2つのパラメータは、平行カップリング長(Lp)とカップリングスペース(S)です。明らかに、信号がカーブ配線で伝送される場合、平行線セグメント間のカップリングは差動モードの形で発生する。Sが小さいほどLpは大きくなり、結合度は大きくなる。このため、伝送遅延の減少や、クロスによる信号品質の大幅な低下を招く可能性があり、そのメカニズムはコモンモードとディファレンシャルモードのクロスの解析を参照することができる。

PCBレイアウトで起こりうる問題、原因、影響

| 問題 | 原因 | 効果 |

| LNA/タンク回路配置(レシーバー) | インダクタの向き | RFフィードスルー |

| ディジェネレーション/πネットワーク配置(送信機) | インダクタの向き | RFフィードスルー |

| πネットワークのレッグ間の共有グラウンド・ビア | 寄生虫経由 | フィードスルー、RFリーク |

| レシーバー・ブロック間の共有グラウンド・ビア | 寄生虫経由 | クロストーク、RFフィードスルー、RFリーク |

| デカップリング・コンデンサー用の長いトレース | 高インピーダンス接続 | デカップリングの低減 |

| 広い部品配置 | 寄生、グランドループの増加 | デチューニング、クロストーク、フィードスルー |

| 送信回路のコリニアートレース | フィルターバイパス、すなわちパワーアンプ(PA)を直接アンテナに接続 | 高調波放射 |

| 上層銅の注入 | 寄生カップリング | RF漏れ、RF干渉 |

| 不連続グランドプレーン | 現在の濃度を戻す | クロストーク、フィードスルー |

| 水晶振動子接続トレース長 | 過剰キャパシタンス | LO周波数プル |

| クリスタル接続トレース分離 | 過剰キャパシタンス | LO周波数プル |

| クリスタルパッド下のグランドプレーン | 過剰キャパシタンス | LO周波数プル |

| 平面PCBトレースインダクタ | インダクタンス制御不良 |