Làm thế nào để tạo ra một bảng mạch PCB tốt

Mọi người đều biết để làm sơ đồ nguyên lý của PCB được thiết kế thành PCB thực, xin đừng đánh giá thấp quá trình này, có rất nhiều điều về nguyên tắc khả thi trong kỹ thuật khó đạt được hoặc một số nhà sản xuất PCB có thể nhận ra và những người khác không đạt được chúng, vì vậy để tạo ra PCB không khó, nhưng để tạo ra một bảng mạch PCB tốt thì không phải là điều dễ dàng. Hai khó khăn lớn trong lĩnh vực vi điện tử là xử lý tín hiệu tần số cao và tín hiệu yếu. Về mặt này, mức độ sản xuất PCB là đặc biệt quan trọng. Cùng một thiết kế sơ đồ, cùng một thành phần, các nhà máy PCB khác nhau làm cho PCB có kết quả khác nhau, vậy làm thế nào để tạo ra một bảng mạch PCB tốt?

1.Làm rõ mục tiêu thiết kế

Nhận nhiệm vụ thiết kế, trước tiên phải làm rõ mục tiêu thiết kế, là bảng PCB thông thường, PCB tần số cao, PCB tín hiệu nhỏ hoặc có cả PCB tần số cao và tín hiệu nhỏ, nếu là PCB thông thường, miễn là làm được Bố trí hợp lý và gọn gàng, kích thước cơ học chính xác, điều đó sẽ ổn thôi.

Khi có nhiều hơn 40 MHz đường tín hiệu trên bảng, cần xem xét đặc biệt đối với các đường tín hiệu này. Nếu tần suất cao hơn, sẽ có nhiều hạn chế nghiêm ngặt hơn về độ dài của dấu vết. Theo lý thuyết mạng tham số phân tán, sự tương tác giữa mạch tốc độ cao và dấu vết của nó là yếu tố quyết định, không thể bỏ qua trong thiết kế hệ thống. Khi tốc độ truyền tăng lên, sự đối lập trên đường tín hiệu sẽ tăng tương ứng và nhiễu xuyên âm giữa các đường tín hiệu liền kề sẽ tăng theo tỷ lệ trực tiếp. Nói chung, mức tiêu thụ điện năng và tản nhiệt của các mạch tốc độ cao cũng rất lớn, vì vậy cần chú ý đầy đủ khi chế tạo PCB tốc độ cao.

Khi có tín hiệu yếu millivolt hoặc thậm chí microvolt trên bảng, các đường tín hiệu này cần được chú ý đặc biệt. Các tín hiệu nhỏ quá yếu để dễ bị nhiễu bởi các tín hiệu mạnh khác. Các biện pháp che chắn thường là cần thiết, nếu không, tỷ lệ tín hiệu trên tạp âm sẽ giảm đi rất nhiều. Vì vậy, tín hiệu hữu ích bị tiếng ồn lấn át và không thể được trích xuất một cách hiệu quả.

Việc gỡ lỗi của bảng cũng nên được xem xét trong giai đoạn thiết kế, không thể bỏ qua vị trí vật lý của điểm kiểm tra, cách ly điểm kiểm tra và các yếu tố khác, vì không thể thêm trực tiếp một số tín hiệu nhỏ và tín hiệu tần số cao đến đầu dò để đo.

Ngoài ra, một số yếu tố liên quan khác cần được xem xét, chẳng hạn như số lớp của bảng, bao bì của các thành phần được sử dụng và độ bền cơ học của bảng. Trước khi tạo bảng PCB, bạn nên có ý tưởng rõ ràng về mục tiêu thiết kế của thiết kế.

2.Hiểu cách bố trí PCB và các yêu cầu định tuyến PCB của các thành phần được sử dụng

Như chúng ta đã biết, một số thành phần đặc biệt có các yêu cầu đặc biệt về bố cục và định tuyến, chẳng hạn như bộ khuếch đại analog được sử dụng trong LOTI và APH, yêu cầu nguồn điện mượt mà, ít gợn sóng. Phần tín hiệu tương tự nhỏ nên được đặt càng xa thiết bị nguồn càng tốt. Trên bo mạch OTI, phần khuếch đại tín hiệu nhỏ được trang bị đặc biệt với vỏ che chắn để che chắn nhiễu điện từ đi lạc. Chip Glink được sử dụng trên bo mạch NTOI áp dụng quy trình ECL, tiêu thụ nhiều điện năng và tỏa nhiều nhiệt. Do đó, phải đặc biệt xem xét vấn đề tản nhiệt trong cách bố trí. Nếu sử dụng tản nhiệt tự nhiên, chip Glink nên được đặt ở nơi không khí lưu thông tương đối thông suốt và nhiệt tỏa ra không thể gây ảnh hưởng lớn đến các chip khác. Nếu bo mạch được trang bị loa hoặc các thiết bị công suất cao khác, nó có thể gây ô nhiễm nghiêm trọng cho nguồn điện, điều này cũng cần được chú ý đầy đủ.

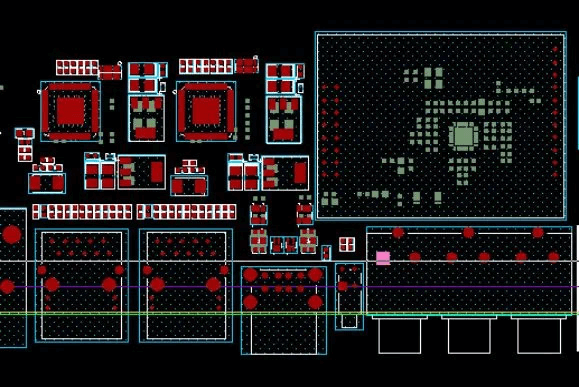

3. Cân nhắc vị trí thành phần

Một trong những yếu tố đầu tiên được xem xét trong thiết kế PCB của các thành phần là hiệu suất điện. Kích thước thực tế (diện tích chiếm dụng và chiều cao) của các thành phần và vị trí tương đối giữa các thành phần phải được xem xét để đảm bảo hiệu suất điện của bảng mạch và tính khả thi và thuận tiện của sản xuất và cài đặt. Đặt các thành phần được kết nối chặt chẽ với nhau càng nhiều càng tốt, đặc biệt là đối với một số đường tốc độ cao và làm cho nó càng ngắn càng tốt. Tách tín hiệu nguồn khỏi các thành phần tín hiệu nhỏ. Trong tiền đề đáp ứng hiệu suất mạch, nhưng cũng cần xem xét các thành phần được đặt gọn gàng, đẹp mắt, dễ kiểm tra, kích thước cơ học của bảng, vị trí ổ cắm, v.v. cũng cần được xem xét nghiêm túc.

Thời gian trễ truyền dẫn của nối đất và kết nối trong các hệ thống tốc độ cao cũng là yếu tố đầu tiên được xem xét trong thiết kế hệ thống. Thời gian truyền dẫn trên đường tín hiệu có ảnh hưởng lớn đến tốc độ chung của hệ thống, đặc biệt đối với các mạch ECL tốc độ cao. Mặc dù bản thân tốc độ của khối mạch tích hợp là rất cao, nhưng việc tăng thời gian trễ do sử dụng các kết nối thông thường trên bo mạch (độ trễ khoảng 2ns cho mỗi chiều dài đường dây 30cm) có thể làm giảm đáng kể tốc độ hệ thống.

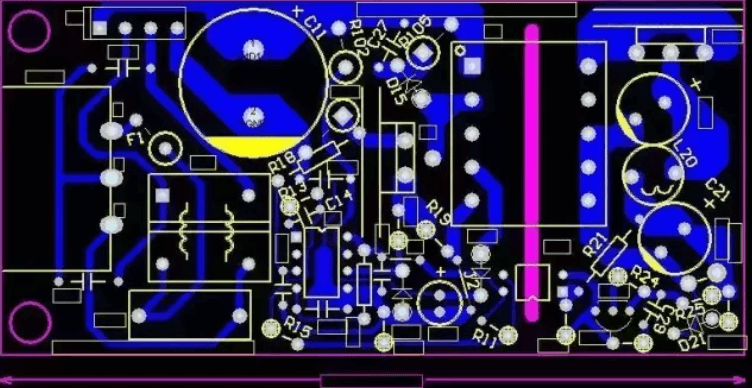

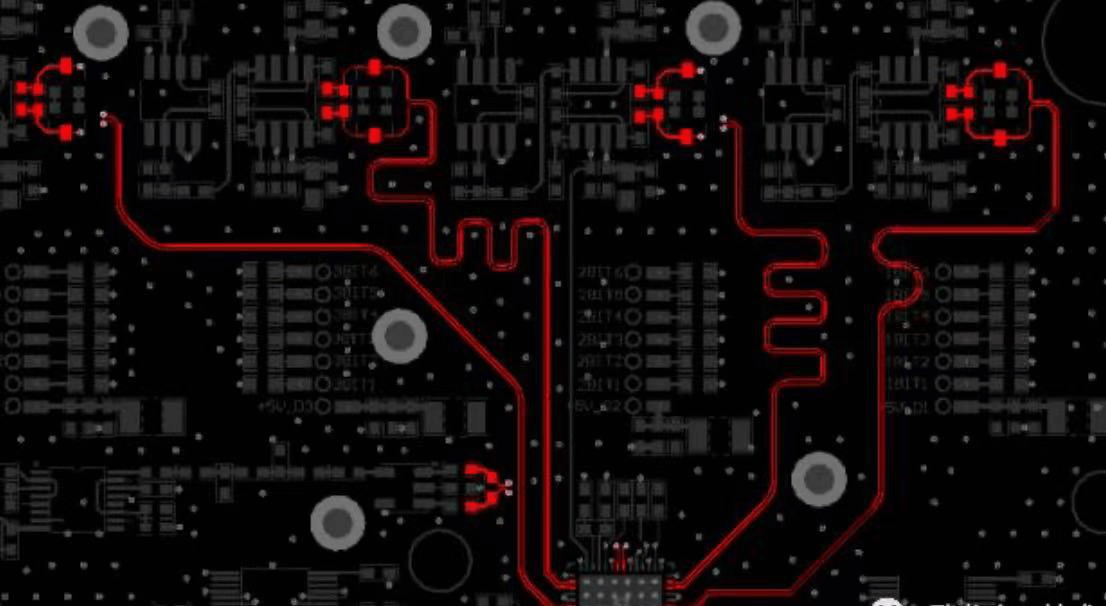

4.PCB định tuyến

Định tuyến PCB là quy trình quan trọng nhất trong toàn bộ thiết kế PCB. Điều này sẽ ảnh hưởng trực tiếp đến hiệu suất của bảng mạch PCB. Trong quá trình thiết kế PCB, việc định tuyến chủ yếu được thực hiện theo các nguyên tắc sau:

(1) Nói chung, đường dây điện và đường dây nối đất nên được thiết kế trước để đảm bảo hiệu suất điện của bảng mạch. Trong phạm vi có thể, hãy cố gắng mở rộng chiều rộng của nguồn điện, đường dây nối đất, tốt nhất là rộng hơn đường dây nguồn, mối quan hệ của chúng là đường dây nối đất > đường dây điện > đường tín hiệu, thông thường, chiều rộng của đường tín hiệu là : 0.2 ~ 0.3mm, chiều rộng tối thiểu lên tới 0.05 ~ 0.07mm, đường dây điện thường là 1.2 ~ 2.5mm. PCB cho mạch kỹ thuật số có thể được sử dụng với dây dẫn nối đất rộng để tạo thành mạch, nghĩa là tạo thành lưới nối đất (không thể sử dụng mặt đất cho các mạch tương tự theo cách này)

(2) Các đường tần số cao nên được đặt cao hơn, đầu vào và đầu ra của đường cạnh phải tránh song song liền kề, để không tạo ra nhiễu phản xạ.

(3) Bất kỳ đường tín hiệu nào cũng không được tạo thành vòng lặp, nếu không thể tránh khỏi, vòng lặp phải càng nhỏ càng tốt; lỗ xuyên qua của đường tín hiệu càng ít càng tốt;(4) Giữ cho các đường chính ngắn và dày, đồng thời thêm lớp bảo vệ ở cả hai bên.

(5) Khi truyền tín hiệu nhạy cảm và tín hiệu dải trường nhiễu qua cáp phẳng, nên sử dụng cách “tiếp đất – tín hiệu – tiếp đất”.

(6) Các điểm kiểm tra nên được dành riêng cho các tín hiệu chính để tạo điều kiện thuận lợi cho việc kiểm tra sản xuất và bảo trì.

(7) Sau khi hoàn thành việc định tuyến sơ đồ, việc định tuyến phải được tối ưu hóa; Đồng thời, sau khi kiểm tra mạng sơ bộ và kiểm tra DRC là chính xác, khu vực không định tuyến sẽ được lấp đầy bằng một đường nối đất và một diện tích lớn bằng đồng được sử dụng làm đường nối đất. Trên bảng mạch in, những nơi không được sử dụng được kết nối với mặt đất dưới dạng đường dây nối đất. Hoặc được làm thành bảng nhiều lớp, nguồn điện, đường dây nối đất đặt trên một lớp riêng biệt.

Yêu cầu định tuyến PCB

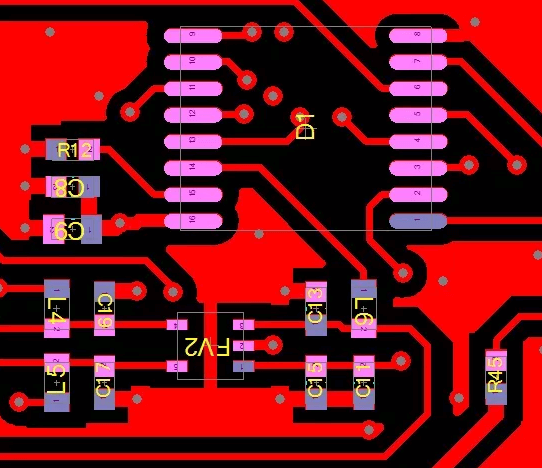

1.Theo dõi

Nói chung, chiều rộng đường tín hiệu là 0.3mm(12mil), chiều rộng đường nguồn là 0.77mm(30mil) hoặc 1.27mm(50mil); Khoảng cách giữa các rãnh, giữa các rãnh và miếng đệm, lớn hơn hoặc bằng 0.33mm(13mil). Trong ứng dụng thực tế, không gian nên được xem xét khi điều kiện cho phép; Khi mật độ rãnh cao, có thể xem xét (nhưng không khuyến nghị) sử dụng hai rãnh giữa các chân IC, chiều rộng của rãnh là 0.254mm(10mil) và khoảng cách của chúng không nhỏ hơn 0.254mm(10mil). Trong những trường hợp đặc biệt, khi các chân thiết bị dày đặc và chiều rộng hẹp, chiều rộng của dòng và khoảng cách dòng có thể được giảm một cách thích hợp.

2. Bàn phím

Các yêu cầu cơ bản đối với pad và via là: đường kính của pad phải lớn hơn 0.6mm so với đường kính của via; Ví dụ: điện trở, tụ điện và mạch tích hợp loại chân cắm đa năng, v.v., sử dụng miếng đệm/thông qua kích thước 1.6mm/0.8mm (63mil/32mil), ổ cắm, chân cắm và đi-ốt 1N4007, v.v., sử dụng 1.8mm/ 1.0mm (71 triệu/39 triệu). Trong ứng dụng thực tế, nó phải được xác định theo kích thước của các thành phần thực tế. Nếu điều kiện cho phép, kích thước của các miếng đệm có thể được tăng lên một cách thích hợp. Các lỗ gắn linh kiện được thiết kế trên bảng mạch PCB phải lớn hơn khoảng 0.2 ~ 0.4mm so với kích thước thực của chân linh kiện.

3.Qua

Thông thường 1.27mm/0.7mm(50mil/28mil); Khi mật độ dòng cao, kích thước của via có thể được giảm xuống một cách thích hợp, nhưng không nên quá nhỏ. Có thể xem xét 1.0mm/0.6mm(40mil/24mil).

4. Yêu cầu về khoảng cách đối với miếng đệm, đường ray và vias

pad và via: ≥ 0.3mm(12mil)pad và pad: ≥ 0.3mm(12mil)pad và track: ≥ 0.3mm(12mil)track và track: ≥ 0.3mm(12mil)Khi mật độ track cao:pad và via : ≥ 0.254mm(10mil)pad và pad: ≥ 0.254mm(10mil)pad và track: ≥ 0.254mm(10mil)track và track: ≥ 0.254mm(10mil)

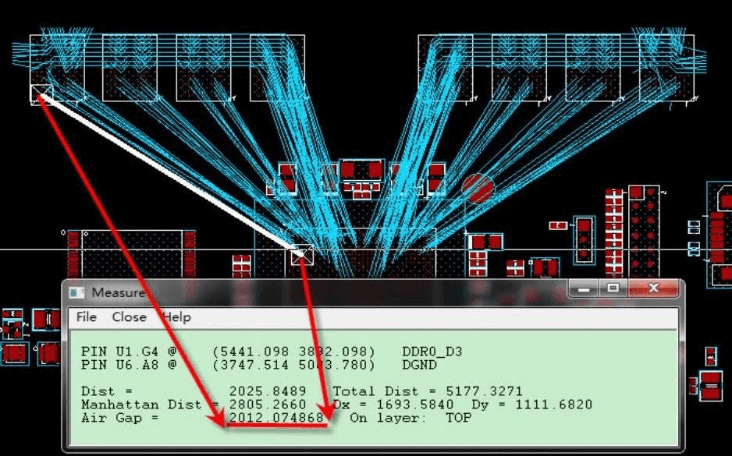

5. Kiểm tra mạng, kiểm tra DRC và kiểm tra cấu trúc

Đầu tiên, với tiền đề rằng thiết kế PCB của sơ đồ mạch là chính xác, hãy kiểm tra mạng mối quan hệ kết nối vật lý giữa tệp mạng PCB được tạo và tệp mạng sơ đồ, đồng thời sửa đổi thiết kế kịp thời theo tệp đầu ra để đảm bảo tính chính xác của mối quan hệ kết nối định tuyến.

Sau khi kiểm tra mạng được thông qua chính xác, hãy tiến hành kiểm tra DRC trên thiết kế PCB và sửa đổi thiết kế theo tệp đầu ra kịp thời để đảm bảo hiệu suất điện của định tuyến PCB. Cuối cùng, cấu trúc lắp đặt cơ học của PCB cần kiểm tra thêm và xác nhận.

Ba kỹ năng định tuyến đặc biệt trong bố cục PCB

1. Định tuyến góc phải

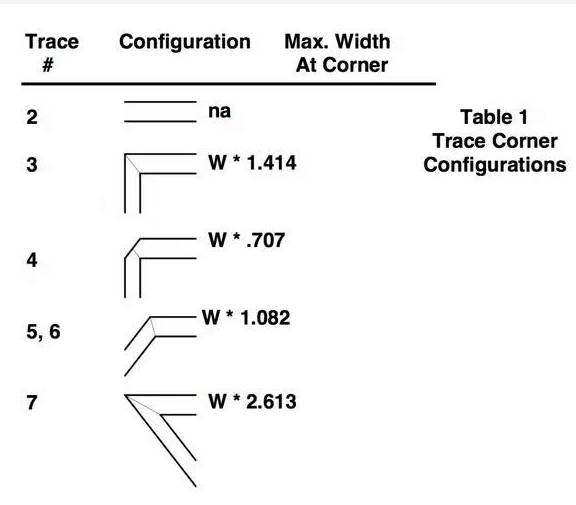

Ảnh hưởng của định tuyến góc vuông đối với tín hiệu chủ yếu được phản ánh ở ba khía cạnh: thứ nhất, góc có thể tương đương với tải điện dung trên đường truyền, làm chậm thời gian tăng; Thứ hai, sự gián đoạn trở kháng sẽ gây ra phản xạ của tín hiệu; Thứ ba là EMI được tạo bởi góc bên phải. Đối với lĩnh vực thiết kế RF trên 10GHz, những góc vuông nhỏ này có thể trở thành đối tượng chính của các bài toán tốc độ cao.

2. Định tuyến vi sai

Tín hiệu vi sai là khi trình điều khiển gửi hai tín hiệu ngược chiều tương đương và bộ thu sẽ so sánh sự khác biệt giữa hai điện áp để xác định xem trạng thái logic là “0” hay “1”. Cặp dây mang tín hiệu vi sai được gọi là tín hiệu vi sai. đường vi sai. So với định tuyến tín hiệu một đầu thông thường, ưu điểm rõ ràng nhất của tín hiệu vi sai phản ánh ở ba khía cạnh sau: 1), khả năng chống nhiễu cao do khả năng ghép nối rất tốt giữa hai đường vi sai khi có nhiễu bên ngoài. Nó có thể ghép nối với cả hai đường cùng một lúc, trong khi đầu nhận chỉ quan tâm đến sự khác biệt giữa hai tín hiệu. Vì vậy, có thể loại bỏ hoàn toàn tiếng ồn bên ngoài phổ biến. Tương tự như vậy, do cực tính của hai tín hiệu ngược nhau nên trường điện từ do chúng phát ra có thể triệt tiêu lẫn nhau. Khớp nối càng gần thì năng lượng điện từ thoát ra bên ngoài càng ít.3), Định vị thời gian chính xác. Do sự thay đổi công tắc của tín hiệu vi sai nằm ở giao điểm của hai tín hiệu, không giống như tín hiệu một đầu thông thường, phụ thuộc vào điện áp ngưỡng cao và thấp để phán đoán, nên nó ít bị ảnh hưởng bởi quá trình và nhiệt độ và có thể giảm lỗi trong thời gian. LVDS (Tín hiệu vi sai điện áp thấp), phổ biến hiện nay, đề cập đến công nghệ báo hiệu vi sai biên độ nhỏ này.

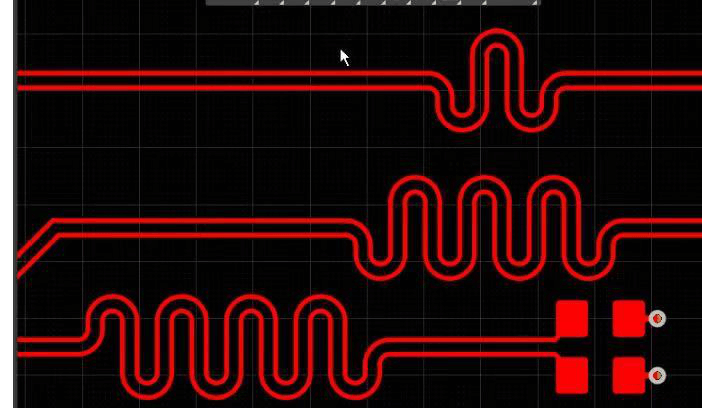

3. Định tuyến cong

Định tuyến cong là một loại phương pháp định tuyến thường được sử dụng trong Bố cục PCB. Mục đích chính của nó là điều chỉnh độ trễ, đáp ứng yêu cầu thiết kế định thời của hệ thống. Hai tham số quan trọng nhất là chiều dài khớp nối song song (Lp) và không gian khớp nối (S). Rõ ràng, khi tín hiệu được truyền trên định tuyến cong, sự ghép nối giữa các đoạn tuyến song song sẽ xảy ra dưới dạng vi sai. S càng nhỏ, Lp càng lớn và mức độ liên kết càng lớn. Điều này có thể dẫn đến giảm độ trễ truyền và giảm đáng kể chất lượng tín hiệu do chéo, cơ chế của nó có thể được tham khảo để phân tích chế độ chung và chéo chế độ vi sai.

Một số sự cố bố trí PCB có thể xảy ra, nguyên nhân và ảnh hưởng

| Vấn đề | Nguyên nhân | Hiệu ứng |

| Bố trí mạch LNA/bể (máy thu) | định hướng cuộn cảm | thông qua RF |

| Thoái hóa/sắp xếp mạng π (máy phát) | định hướng cuộn cảm | thông qua RF |

| Vias mặt đất được chia sẻ giữa các chân của mạng π | Thông qua ký sinh trùng | Thông qua, rò rỉ RF |

| Vias mặt đất được chia sẻ giữa các khối máy thu | Thông qua ký sinh trùng | Xuyên âm, truyền dẫn RF, rò rỉ RF |

| Dấu vết dài để tách tụ điện | Kết nối trở kháng cao hơn | Giảm tách rời |

| Vị trí thành phần rộng | Tăng ký sinh trùng, vòng đất | Detuning, nhiễu xuyên âm, feedthrough |

| Vết cộng tuyến trong mạch phát | Bỏ qua bộ lọc, tức là, bộ khuếch đại công suất (PA) trực tiếp tới ăng-ten | bức xạ sóng hài |

| Đổ đồng lớp trên cùng | khớp nối ký sinh | Rò rỉ RF, nhiễu RF |

| Mặt đất không liên tục | Trả về nồng độ hiện tại | Nhiễu xuyên âm, xuyên âm |

| Độ dài dấu vết kết nối tinh thể | điện dung dư thừa | Kéo tần số LO |

| Tách dấu vết kết nối tinh thể | điện dung dư thừa | Kéo tần số LO |

| Máy bay mặt đất dưới tấm pha lê | điện dung dư thừa | Kéo tần số LO |

| Cuộn cảm dấu vết PCB phẳng | Kiểm soát điện cảm kém |